Verifikasi dan Validasi Model

Verifikasi dan Validasi model

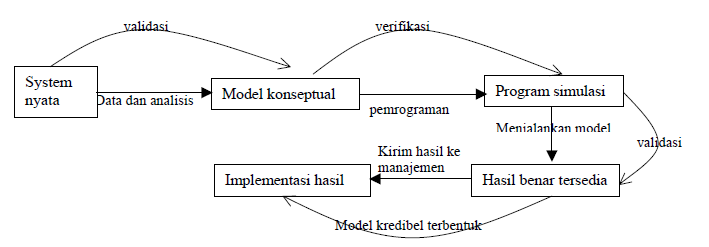

Dalam membangun suatu model simulasi kita harus memperhatikan dan memastikan bahwa model simulasi yang akan dibangun harus kredibel. Representasi kredibel sistem nyata oleh model simulasi ditunjukkan oleh verifikasi dan validasi model.

Pengertian verifikasi menurut para ahli

Menurut Hoover dan Perry 1989

Verifikasi merupakan proses pemeriksaan kesesuaian model logika operasional dengan logika diagram alur atau dapat disederhanakan dengan “apakah terdapat kesalahan dalam program?”.Menurut Law dan Kelton 1991

Verifikasi merupakan suatu proses untuk memeriksa kesesuaian jalannya program computer simulasi dengan yang diinginkan dengan cara melakukan pemeriksaan program computer, selain itu verifikasi dapat diartikan sebagai proses penerjemahan model simulasi konseptual kedalam bahasa pemrograman secara benar.

Pengertian validasi menurut para ahli

Menurut Hoover dan Perry 1989

Validasi adalah proses penentuan apakah model, sebagai konseptualisasi atau abstraksi, merupakan representasi berarti dan akurat dari sistem nyata?Menurut Law dan Kelton 1991

Validasi adalah penentuan apakah mode konseptual simulasi (sebagai tandingan program komputer) adalah representasi akurat dari sistem nyata yang sedang dimodelkan.

Verifikasi bertujuan untuk membuktikan bahwa sesuatu ada atau benar, atau untuk memastikan bahwa sesuatu adalah benar (Verify : to prove that something exists or is true, or to make certain that something is correct), sedangkan validasi bertujuan untuk membuat sesuatu yang resmi diterima atau disetujui, terutama setelah memeriksanya (Validate : to make something officially acceptable or approved, especially after examining it) (Cambridge Dictionaries Online, 2011).

Aturan verifikasi dan validasi dalam simulasi

Dalam melakukan verifikasi dan validasi, terdapat beberapa hal yang harus diperhatikan, berikut merupakan penjelasan lengkapnya:

Verifikasi

Terdapat beberapa hal yang harus diperhatikan dalam melakukan verifikasi pada model logika, diantaranya:

• Apakah kejadian telah direpresentasikan dengan benar?

• Rumus matematika dan relasi apakah sudah benar?

• Ukuran statistic apakah sudah dirumuskan dengan benar?

Terdapat beberapa hal yang harus diperhatikan dalam melakukan verifikasi pada model computer atau simulasi, diantaranya:

• Apakah semua aspek mode logika telah dimuat oleh kode computer?

• Apakah perhitungan statistic dan rumus telah dilakukan dengan benar?

• Apakah model mengandung kesalahan pengkodean?

Validasi

Terdapat beberapa hal yang harus diperhatikan dalam melakukan validasi pada model konseptual, diantaranya:

• Sudahkah semua elemen, kejadian dan relasi yang sesuai terdapat didalam model?

• Apakah pertanyaan pemodelan sudah dapat dijawab dengan model?

Terdapat beberapa hal yang harus diperhatikan dalam melakukan validasi pada model logika, diantaranya:

• Apakah semua kejadian yang terdapat pada model konseptual telah dimuat di dalam model?

• Apakah semua relasi yang terdapat dalam model konseptual telah dimuat didalam model?

Terdapat beberapa hal yang harus diperhatikan dalam melakukan validasi pada model computer atau simulasi, diantaranya:

• Apakah model computer benar merupakan representasi dari system nyata?

• Apakah model computer dapat melakukan duplikasi kinerja system nyata?

• Apakah output dari model computer mempunyai kredibilitas dengan ahli system dan pembuat keputusan?

Sumber :

Verifikasi dan Validasi Model Simulasi, Analisis Output (tugas_mosi_kel 3)

https://andihasad.files.wordpress.com/2011/11/verifikasi-dan-validasi-dalam-simulasi-model.pdf

Cambridge University Press. 2011. Cambridge Dictionaries Online. http://dictionary.cambridge.org/ diakses pada 1 Oktober 2011.

https://andihasad.files.wordpress.com/2011/11/verifikasi-dan-validasi-dalam-simulasi-model.pdf.

Recent Comments